вопрос корифеям логических анализаторов:

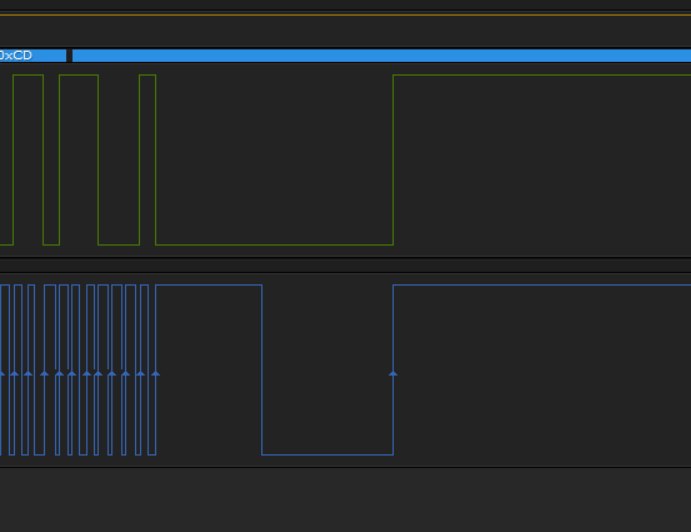

вот есть всякие проприетарные saleae, DSlogic, USBee,

сделанные по принципу FX2+FPGA+SDRAM

есть sigrok, который позволяет использовать свободные прошивки под эту схему, не только FX2, но и похоже FPGA:

https://sigrok.org/wiki/Fpgalafwвопросов собственно несколько (если кто-то ковырял эту тему:

1. USB API (FX2 upstream) sigrok - это что-то своё или реверсенное из проприетарщины, перечисленной выше

2. PIPE API (FPGA-to-FX2) sigrok - это что-то своё или базирующееся на, например, ранних (открытых) версиях протокола DSlogic?

т.е. интересует возможность использования оригинального проприетарного ПО со своим комбайном: для этого надо знать PIPE API (FPGA-to-FX2), чтобы со стороны FPGA поддержать (в своей кастомной прошивке) этот API