E

Size: a a a

2020 October 08

Нормальный фаервол из коробки магическим образом ничего не блокирует. Особенно исходняк.

Именно! Любой фаервол по дефолту или не фильтрует или имеет средне-общие настройки как тот же виндовый.

E

что такое "Всё" может не лью , как бы откуда ты знаешь ?

То есть ты знаешь что исходящий трафик вообще никак не фильтруется и тебе это норм?

DO

То есть ты знаешь что исходящий трафик вообще никак не фильтруется и тебе это норм?

начнем с начала , что фильтровать и зачем ?

DO

система работает не стабильно ? - Нет все в порядке

S

https://adoredtv.com/exclusive-intel-sapphire-rapids-to-feature-chiplets-hbm2-400-watt-tdp-coming-in-2021/

блин, неужели быстрая память рядом с процом появится скоро

According to our information, Sapphire Rapids will be using a multi tile (that is, MCM or chiplet) design and will support HBM2.

...

Alongside 4 CPU dies, there can exist 4 HBM2e stacks with a total capacity of up to 64 GB and a total bandwidth of up to 1 TB/s. This kind of bandwidth could enable some impressive performance, let down only by the 10nm(+++) node which restricts Intel’s volume and CPU performance. Additionally, the HBM2e can work with the DDR5 memory in several modes: flat, caching/2LM, and hybrid.

блин, неужели быстрая память рядом с процом появится скоро

A

А кто нибуть может проверить с какой версии Juniper EX, начал поддерживать ARP Probe (RFC 5227) и есть ли у этой фичи зависимость от железа (у меня ex4550)?

K

Наша песня хороша: Microsoft снова хочет купить Nokia.

Сетевой бизнес Nokia привлекателен для многих, поскольку Nokia Networks — один из крупнейших производителей и поставщиков телекоммуникационного оборудования: http://amp.gs/LdVL

Сетевой бизнес Nokia привлекателен для многих, поскольку Nokia Networks — один из крупнейших производителей и поставщиков телекоммуникационного оборудования: http://amp.gs/LdVL

VK

https://adoredtv.com/exclusive-intel-sapphire-rapids-to-feature-chiplets-hbm2-400-watt-tdp-coming-in-2021/

блин, неужели быстрая память рядом с процом появится скоро

According to our information, Sapphire Rapids will be using a multi tile (that is, MCM or chiplet) design and will support HBM2.

...

Alongside 4 CPU dies, there can exist 4 HBM2e stacks with a total capacity of up to 64 GB and a total bandwidth of up to 1 TB/s. This kind of bandwidth could enable some impressive performance, let down only by the 10nm(+++) node which restricts Intel’s volume and CPU performance. Additionally, the HBM2e can work with the DDR5 memory in several modes: flat, caching/2LM, and hybrid.

блин, неужели быстрая память рядом с процом появится скоро

догоняют нетворк вендоров по чуть )

R

Демократы в США выпустили большой доклад о монополии Google, Facebook, Apple, Amazon.

Конгрессмены предложили разделить IT-корпорации, запретив им покупать конкурентов и владеть смежным бизнесом. Например, принудительно отделить YouTube от Google и Instagram от Facebook.

Все четыре компании уже ответили: они считают, что это только навредит рынку.

https://tjournal.ru/news/220602

Конгрессмены предложили разделить IT-корпорации, запретив им покупать конкурентов и владеть смежным бизнесом. Например, принудительно отделить YouTube от Google и Instagram от Facebook.

Все четыре компании уже ответили: они считают, что это только навредит рынку.

https://tjournal.ru/news/220602

VK

Демократы в США выпустили большой доклад о монополии Google, Facebook, Apple, Amazon.

Конгрессмены предложили разделить IT-корпорации, запретив им покупать конкурентов и владеть смежным бизнесом. Например, принудительно отделить YouTube от Google и Instagram от Facebook.

Все четыре компании уже ответили: они считают, что это только навредит рынку.

https://tjournal.ru/news/220602

Конгрессмены предложили разделить IT-корпорации, запретив им покупать конкурентов и владеть смежным бизнесом. Например, принудительно отделить YouTube от Google и Instagram от Facebook.

Все четыре компании уже ответили: они считают, что это только навредит рынку.

https://tjournal.ru/news/220602

эти могут. Standart Oil же разделили )

VV

Ну, уж проебали...

VA

Yaroslav

на рублевке - сетевики там обычно селятся

Y

точно видно что на удаленке кстати

Y

Виктор и FD

VA

все новое - хорошо забытое старое)

VK

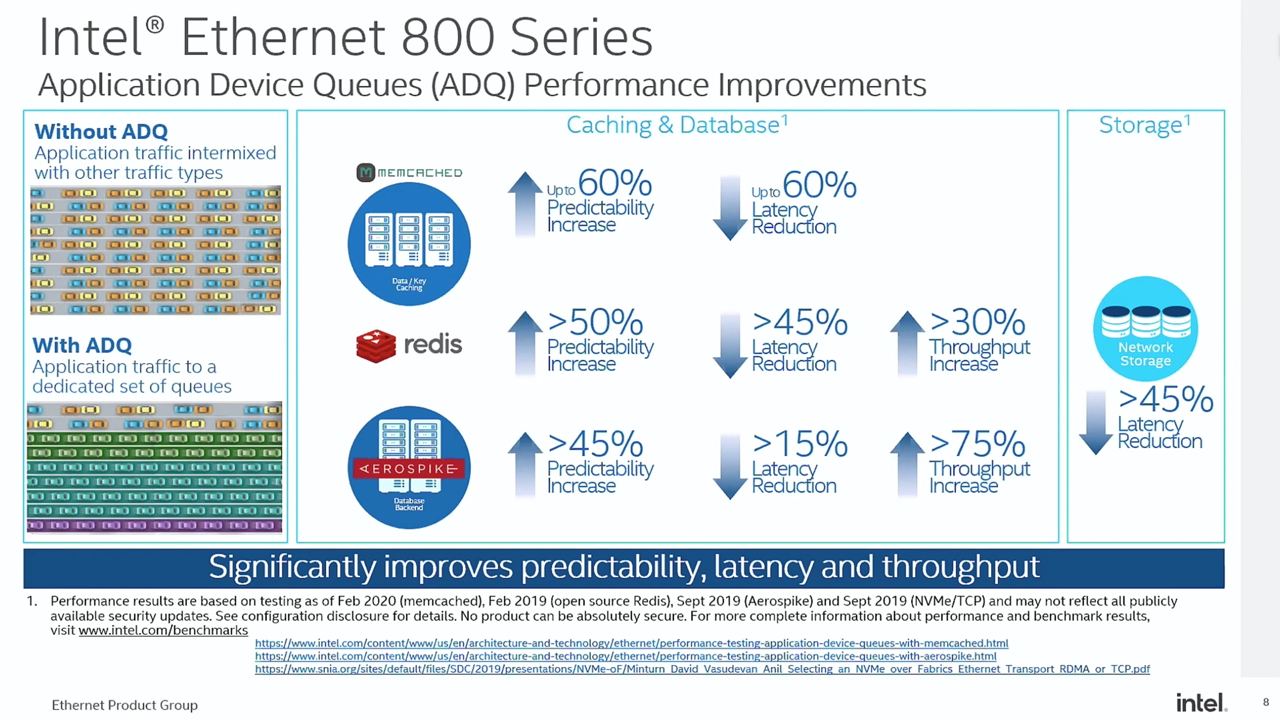

о, интел очереди завезли в сетевухи

VK